Nā noi RF hana kiʻekiʻe 12 ʻīniha SiC Substrate N Type Nui

Nā palena loea

| ʻO ke kikoʻī o ka substrate Silicon Carbide (SiC) 12 ʻīniha | |||||

| Papa | Hana ʻana o ZeroMPD Papa (Papa Z) | Hana Maʻamau Papa (Papa P) | Papa Dummy (Papa D) | ||

| Anawaena | 3 0 0 mm~1305mm | ||||

| Mānoanoa | 4H-N | 750μm±15 μm | 750μm±25 μm | ||

| 4H-SI | 750μm±15 μm | 750μm±25 μm | |||

| Hoʻonohonoho Wafer | ʻO ke axis ma waho: 4.0° i ka ʻaoʻao <1120 >±0.5° no 4H-N, Ma ke axis: <0001>±0.5° no 4H-SI | ||||

| Ka nui o ka micropipe | 4H-N | ≤0.4cm-2 | ≤4cm-2 | ≤25cm-2 | |

| 4H-SI | ≤5cm-2 | ≤10cm-2 | ≤25cm-2 | ||

| Ke kū'ē ʻana | 4H-N | 0.015~0.024 Ω·cm | 0.015~0.028 Ω·cm | ||

| 4H-SI | ≥1E10 Ω·cm | ≥1E5 Ω·cm | |||

| Kūlana Pālahalaha Mua | {10-10} ±5.0° | ||||

| Ka Lōʻihi Palahalaha Mua | 4H-N | ʻAʻohe | |||

| 4H-SI | ʻOki | ||||

| Hoʻokaʻawale ʻana i ka lihi | 3 mm | ||||

| LTV/TTV/Kakaka/Warp | ≤5μm/≤15μm/≤35 μm/≤55 μm | ≤5μm/≤15μm/≤35 □ μm/≤55 □ μm | |||

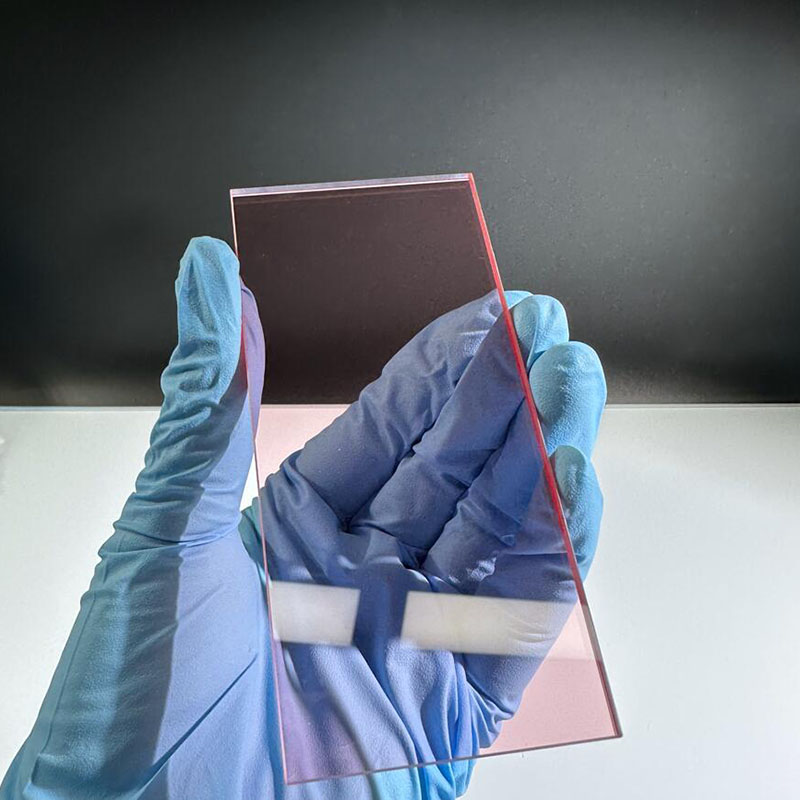

| ʻOʻoleʻa | Polani Ra≤1 nm | ||||

| CMP Ra≤0.2 nm | Ra≤0.5 nm | ||||

| Nā Māwae Lihi e ka Mālamalama Ikaika Kiʻekiʻe Nā Papa Hex Ma o ke Kukui Ikaika Kiʻekiʻe Nā wahi Polytype e ka mālamalama ikaika kiʻekiʻe Nā Hoʻokomo Kalapona ʻIke Nā ʻōpala ʻili Silicon e ka mālamalama ikaika kiʻekiʻe | ʻAʻohe ʻĀpana hōʻuluʻulu ≤0.05% ʻAʻohe ʻĀpana hōʻuluʻulu ≤0.05% ʻAʻohe | Ka lōʻihi hui ≤ 20 mm, ka lōʻihi hoʻokahi ≤2 mm ʻĀpana hōʻuluʻulu ≤0.1% ʻĀpana hōʻuluʻulu ≤3% ʻĀpana hōʻuluʻulu ≤3% Ka lōʻihi huina ≤1 × ke anawaena wafer | |||

| Nā ʻāpana lihi e ka mālamalama ikaika kiʻekiʻe | ʻAʻohe mea i ʻae ʻia ≥0.2mm ka laulā a me ka hohonu | 7 i ʻae ʻia, ≤1 mm kēlā me kēia | |||

| (TSD) Hoʻoneʻe ʻana i ka wili wili | ≤500 kenimika-2 | ʻAʻohe | |||

| (BPD) Ka neʻe ʻana o ka mokulele kumu | ≤1000 kenimika-2 | ʻAʻohe | |||

| Ka haumia ʻana o ka ʻili Silicon e ka mālamalama ikaika kiʻekiʻe | ʻAʻohe | ||||

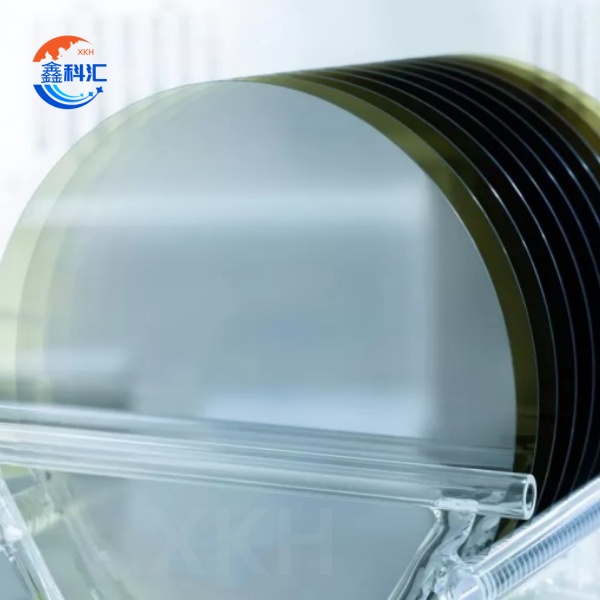

| Ka hoʻopili ʻana | Kaseta Wafer Multi-wafer a i ʻole ka ipu Wafer hoʻokahi | ||||

| Nā memo: | |||||

| 1 Pili nā palena kīnā i ka ʻili wafer holoʻokoʻa koe wale nō ka ʻāpana hoʻokoe lihi. Pono e nānā ʻia nā ʻōpala ma ka maka Si wale nō. 3 Mai nā wafers i kālai ʻia ʻo KOH wale nō ka ʻikepili dislocation. | |||||

Nā Hiʻohiʻona Koʻikoʻi

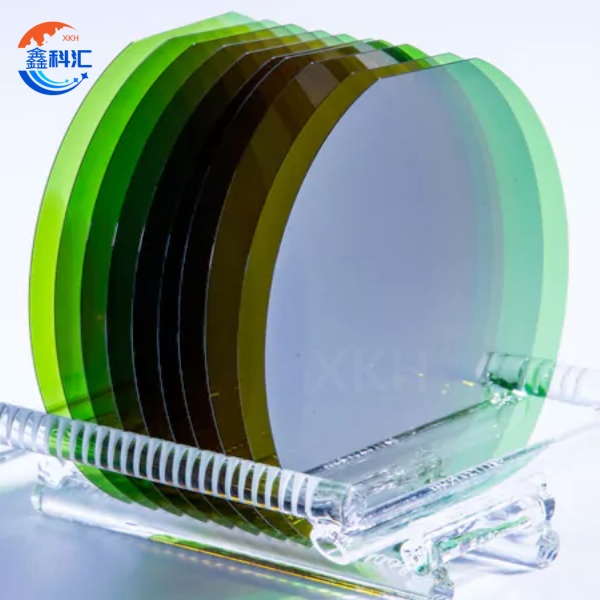

1. Pōmaikaʻi Nui: Hāʻawi ka substrate SiC 12-'īniha (12-'īniha silicon carbide substrate) i kahi wahi wafer hoʻokahi nui aʻe, e hiki ai ke hana ʻia nā ʻāpana he nui aʻe no kēlā me kēia wafer, a laila e hōʻemi ana i nā kumukūʻai hana a hoʻonui i ka hua.

2. Mea Hana Kiʻekiʻe: ʻO ke kūpaʻa wela kiʻekiʻe o ka Silicon carbide a me ka ikaika o ke kahua haki kiʻekiʻe e hoʻolilo i ka substrate 12-'īniha i kūpono no nā noi voltage kiʻekiʻe a me ke alapine kiʻekiʻe, e like me nā inverters EV a me nā ʻōnaehana hoʻouka wikiwiki.

3. Hoʻohālikelike Hana: ʻOiai ke kiʻekiʻe o ka paʻakikī a me nā pilikia hana o SiC, hoʻokō ka substrate SiC 12-'īniha i nā hemahema ʻili haʻahaʻa ma o nā ʻano ʻoki a me ka polishing i hoʻomaikaʻi ʻia, e hoʻomaikaʻi ana i ka hua o ka hāmeʻa.

4. Hoʻokele Wela Kiʻekiʻe: Me ka conductivity thermal ʻoi aku ka maikaʻi ma mua o nā mea silicon-based, hoʻoponopono pono ka substrate 12-'īniha i ka hoʻolaha wela i nā mea hana mana kiʻekiʻe, e hoʻolōʻihi ana i ke ola o nā lako.

Nā Noi Nui

1. Nā Kaʻa Uila: ʻO ka substrate SiC 12-'īniha (12-'īniha silicon carbide substrate) kahi ʻāpana koʻikoʻi o nā ʻōnaehana hoʻokele uila hanauna hou, e hiki ai i nā inverters kiʻekiʻe-kūpono e hoʻonui i ka laulā a hoʻemi i ka manawa hoʻouka.

2. Nā Kikowaena Kumu 5G: Kākoʻo nā substrates SiC nui i nā polokalamu RF alapine kiʻekiʻe, e hoʻokō ana i nā koi o nā kikowaena kumu 5G no ka mana kiʻekiʻe a me ka pohō haʻahaʻa.

3. Nā Lako Mana ʻOihana: I loko o nā inverters solar a me nā grids akamai, hiki i ka substrate 12-'īniha ke kū i nā voltages kiʻekiʻe aʻe me ka hoʻemi ʻana i ka pohō ikehu.

4. Nā Mea Uila Kūʻai: Hiki i nā mea hoʻoili wikiwiki e hiki mai ana a me nā lako mana kikowaena ʻikepili ke hoʻohana i nā substrates SiC 12-'īniha e hoʻokō ai i ka nui liʻiliʻi a me ka pono kiʻekiʻe.

Nā lawelawe a XKH

He loea mākou i nā lawelawe hana i hoʻopilikino ʻia no nā substrates SiC 12-'īniha (nā substrates silicon carbide 12-'īniha), me:

1. ʻOki ʻoki a me ka poli ʻana: Hana ʻana i ka substrate haʻahaʻa-pōʻino, pālahalaha kiʻekiʻe i hoʻopilikino ʻia i nā koi o ka mea kūʻai aku, e hōʻoiaʻiʻo ana i ka hana paʻa o ka hāmeʻa.

2. Kākoʻo ulu ʻana o Epitaxial: Nā lawelawe wafer epitaxial kiʻekiʻe e hoʻolalelale i ka hana ʻana o nā ʻāpana.

3. Hoʻohālikelike Pūʻulu Liʻiliʻi: Kākoʻo i ka hōʻoia R&D no nā ʻoihana noiʻi a me nā ʻoihana, e hoʻopōkole ana i nā pōʻaiapuni hoʻomohala.

4. Kūkākūkā ʻenehana: Nā hoʻonā hoʻopau-a-hopena mai ke koho ʻana i nā mea a hiki i ka hoʻonui ʻana i ke kaʻina hana, e kōkua ana i nā mea kūʻai aku e lanakila i nā pilikia hana SiC.

Inā no ka hana nui ʻana a i ʻole ka hoʻopilikino kūikawā ʻana, kūlike kā mākou lawelawe substrate SiC 12-ʻīniha me kāu mau pono papahana, e hoʻoikaika ana i nā holomua ʻenehana.