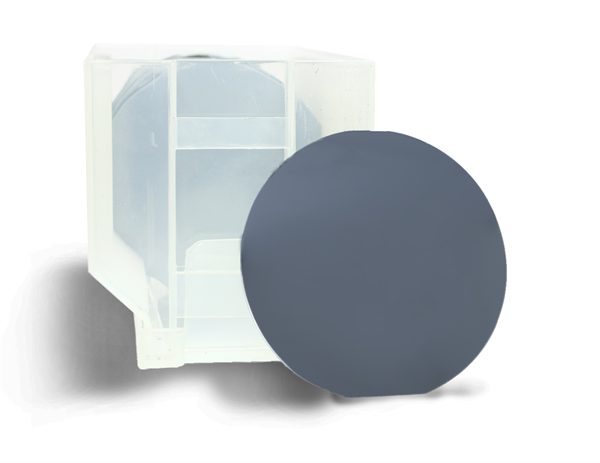

ʻO ke substrate SiC ʻano P-ʻano 4H/6H-P 3C-N 4'iniha me ka mānoanoa o 350um Papa hana Papa Dummy

Papa ʻaina palena 4 iniha SiC substrate P-type 4H/6H-P 3C-N

4 ʻīniha ke anawaena SiliconʻO ka Carbide (SiC) Substrate Nā kikoʻī

| Papa | Hana ʻana o ka Zero MPD Papa (Z Papa) | Hana Maʻamau Papa (P Papa) | Papa Dummy (D Papa) | ||

| Anawaena | 99.5 mm~100.0 mm | ||||

| Mānoanoa | 350 μm ± 25 μm | ||||

| Hoʻonohonoho Wafer | Ma waho o ke axis: 2.0°-4.0° i ka ʻaoʻao [11]20] ± 0.5° no 4H/6H-P, Oaxis n:〈111〉± 0.5° no 3C-N | ||||

| Ka nui o ka micropipe | 0 kenimika-2 | ||||

| Ke kū'ē ʻana | ʻano-p 4H/6H-P | ≤0.1 Ωꞏcm | ≤0.3 Ωꞏcm | ||

| ʻano-n 3C-N | ≤0.8 mΩꞏcm | ≤1 m Ωꞏcm | |||

| Kūlana Pālahalaha Mua | 4H/6H-P | - {1010} ± 5.0° | |||

| 3C-N | - {110} ± 5.0° | ||||

| Ka Lōʻihi Palahalaha Mua | 32.5 mm ± 2.0 mm | ||||

| Ka Lōʻihi Pālahalaha Lua | 18.0 mm ± 2.0 mm | ||||

| Kūlana Pālahalaha Lua | Ke alo Silicon i luna: 90° CW. mai Prime flat±5.0° | ||||

| Hoʻokaʻawale ʻana i ka lihi | 3 mm | 6 mm | |||

| LTV/TTV/Kakaka/Warp | ≤2.5 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||

| ʻOʻoleʻa | Polani Ra≤1 nm | ||||

| CMP Ra≤0.2 nm | Ra≤0.5 nm | ||||

| Nā Māwae Lihi e ka Mālamalama Ikaika Kiʻekiʻe | ʻAʻohe | Ka lōʻihi hui ≤ 10 mm, ka lōʻihi hoʻokahi ≤2 mm | |||

| Nā Papa Hex Ma o ke Kukui Ikaika Kiʻekiʻe | ʻĀpana hōʻuluʻulu ≤0.05% | ʻĀpana hōʻuluʻulu ≤0.1% | |||

| Nā wahi Polytype e ka mālamalama ikaika kiʻekiʻe | ʻAʻohe | ʻĀpana hōʻuluʻulu ≤3% | |||

| Nā Hoʻokomo Kalapona ʻIke | ʻĀpana hōʻuluʻulu ≤0.05% | ʻĀpana hōʻuluʻulu ≤3% | |||

| Nā ʻōpala ʻili Silicon e ka mālamalama ikaika kiʻekiʻe | ʻAʻohe | Ka lōʻihi huina ≤1 × ke anawaena wafer | |||

| Kiʻekiʻe nā ʻāpana lihi ma o ka mālamalama ikaika | ʻAʻohe mea i ʻae ʻia ≥0.2mm ka laulā a me ka hohonu | 5 i ʻae ʻia, ≤1 mm kēlā me kēia | |||

| Ka haumia ʻana o ka ʻili Silicon ma o ka ikaika kiʻekiʻe | ʻAʻohe | ||||

| Ka hoʻopili ʻana | Kaseta Wafer Multi-wafer a i ʻole ka Pahu Wafer Hoʻokahi | ||||

Nā memo:

※Pili nā palena kīnā i ka ʻili wafer holoʻokoʻa koe wale nō ka ʻāpana i hoʻokaʻawale ʻia ma ka lihi. # Pono e nānā ʻia nā ʻōpala ma ka ʻaoʻao Si wale nō.

Hoʻohana nui ʻia ka substrate SiC ʻano-P 4H/6H-P 3C-N 4-'īniha me ka mānoanoa o 350 μm i ka hana ʻana i nā mea uila a me nā mea mana holomua. Me ka conductivity thermal maikaʻi loa, ka voltage breakdown kiʻekiʻe, a me ke kūpaʻa ikaika i nā kaiapuni koʻikoʻi, kūpono kēia substrate no nā mea uila mana hana kiʻekiʻe e like me nā kuapo voltage kiʻekiʻe, nā inverters, a me nā mea RF. Hoʻohana ʻia nā substrates papa hana i ka hana nui, e hōʻoiaʻiʻo ana i ka hana pono a pololei hoʻi o nā mea hana, he mea koʻikoʻi ia no nā mea uila mana a me nā noi alapine kiʻekiʻe. Ma ka ʻaoʻao ʻē aʻe, hoʻohana nui ʻia nā substrates dummy-grade no ka hoʻoponopono ʻana i ke kaʻina hana, ka hoʻāʻo ʻana i nā lako, a me ka hoʻomohala ʻana i nā prototype, e kōkua ana i ka mālama ʻana i ka kaohi maikaʻi a me ke kūlike o ke kaʻina hana i ka hana semiconductor.

KikoʻīʻO nā pono o nā substrates composite N-type SiC e komo pū ana

- Ka Hoʻokele Wera KiʻekiʻeʻO ka hoʻopuehu wela kūpono e kūpono ai ke substrate no nā noi wela kiʻekiʻe a me ka mana kiʻekiʻe.

- Ka Uila Haʻihaʻi KiʻekiʻeKākoʻo i ka hana uila kiʻekiʻe, e hōʻoiaʻiʻo ana i ka hilinaʻi i nā mea uila mana a me nā polokalamu RF.

- Ke kū'ē ʻana i nā wahi ʻino: Paʻa i nā kūlana koʻikoʻi e like me ke kiʻekiʻe o nā mahana a me nā wahi ʻino, e hōʻoiaʻiʻo ana i ka hana lōʻihi.

- Pololei Papa Hana: Hōʻoia i ka hana kiʻekiʻe a me ka hilinaʻi i ka hana nui ʻana, kūpono no nā noi mana holomua a me RF.

- Papa Hoʻāʻo Dummy no ka Hoʻāʻo ʻana: Hiki ke hoʻololi pololei i ke kaʻina hana, ka hoʻāʻo ʻana i nā lako, a me ke ʻano hana prototype me ka ʻole o ka hoʻopilikia ʻana i nā wafers papa hana.

Ma keʻano holoʻokoʻa, hāʻawi ka substrate SiC ʻano-P 4H/6H-P 3C-N 4-'īniha me ka mānoanoa o 350 μm i nā pono koʻikoʻi no nā noi uila hana kiʻekiʻe. ʻO kona conductivity thermal kiʻekiʻe a me ka voltage breakdown e kūpono ia no nā wahi mana kiʻekiʻe a me nā wahi wela kiʻekiʻe, ʻoiai ʻo kona kūpaʻa ʻana i nā kūlana ʻino e hōʻoiaʻiʻo ana i ka lōʻihi a me ka hilinaʻi. Hōʻoia ka substrate papa hana i ka hana pololei a kūlike i ka hana nui o nā mea uila mana a me nā mea RF. I kēia manawa, he mea nui ka substrate dummy-grade no ka calibration kaʻina hana, ka hoʻāʻo ʻana i nā lako, a me ka prototyping, e kākoʻo ana i ka kaohi maikaʻi a me ke kūlike i ka hana semiconductor. ʻO kēia mau hiʻohiʻona e hana i nā substrates SiC i mea maʻalahi loa no nā noi holomua.

Kiʻikuhi kikoʻī